Quantum-Safe Networks Are No Longer Theoretical

The telecom industry is entering a phase in which quantum security is no longer a laboratory topic but an operational and strategic issue for networks, supply chains, and regulation.

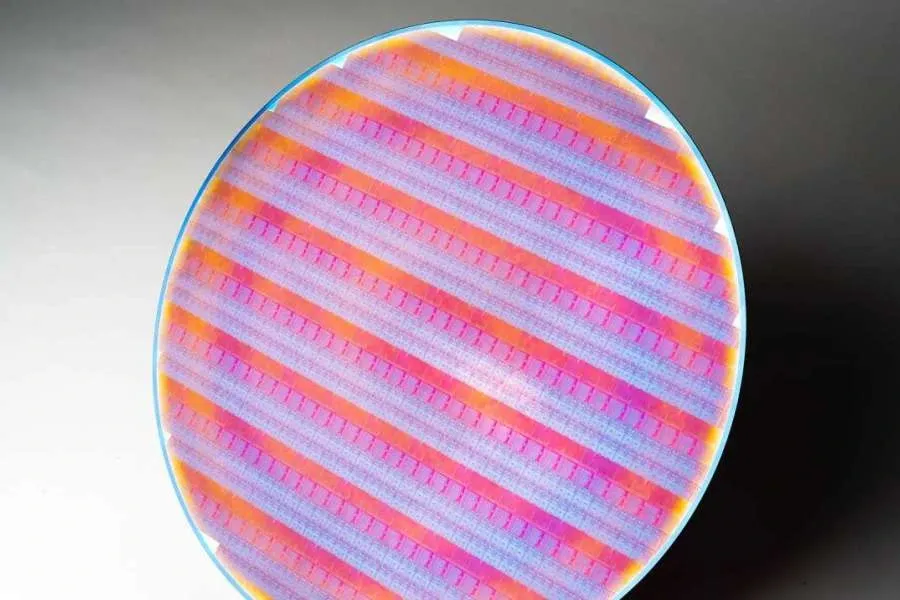

Intel is the first in the industry to implement backside power delivery on a product-like test chip, achieving higher performance. PowerVia, which will be introduced on the Intel 20A process node in the first half of 2024, is Intel’s backside power delivery solution. It solves the growing issue of interconnect bottlenecks in area scaling by moving power routing to the backside of a wafer.

“PowerVia is a major milestone in our aggressive ‘five nodes in four years’ strategy and on our path to achieving a trillion transistors in a package in 2030. Using a trial process node and subsequent test chip-enabled us to de-risk backside power for our leading process nodes, placing Intel a node ahead of competitors in bringing backside power delivery to market,“ said Ben Sell, Intel vice president of Technology Development.

Intel decoupled the development of PowerVia from transistor development to ensure its readiness for silicon implementation based on Intel 20A and Intel 18A process nodes. PowerVia was tested on its own internal test node to debug and ensure the good functionality of the technology before its integration with RibbonFET in Intel 20A. After fabrication and testing on a silicon test chip, PowerVia was confirmed to bring a remarkably efficient use of chip resources with greater than 90% cell utilization and major transistor scaling, enabling chip designers to achieve performance and efficiency gains in their products.

PowerVia is the first to solve the growing interconnect bottleneck issue for chip designers. Surging use cases, including AI and graphics, require smaller, denser, and more powerful transistors to meet ever-growing computing demands. Today and for the past many decades, power and signal lines within a transistor’s architecture have competed for the same resources. By separating the two, chips can increase performance and energy efficiency, and deliver better results for customers. Backside power delivery is vital to transistor scaling, enabling chip designers to increase transistor density without sacrificing resources to deliver more power and performance than ever.